KV260 手元にあるので Pcam 5C とつなげてみる。FPGA の部屋のblogをそのまま1~4までやるとうまくいくよ。

git clone を実行

もともとの Adam Taylor さんのプロジェクトを clone する。名前の一部が Kira になっているところがお茶目。

プロジェクトの作成~インプリメンテーション

Vivado 2021.1 を起動後、bd.tcl を実行しプロジェクトを作成する。Create HDL Wrapper ... でトップモジュールを作って、io.xdc の制約をインポート。その後、インプリメンテーションまで実行する。

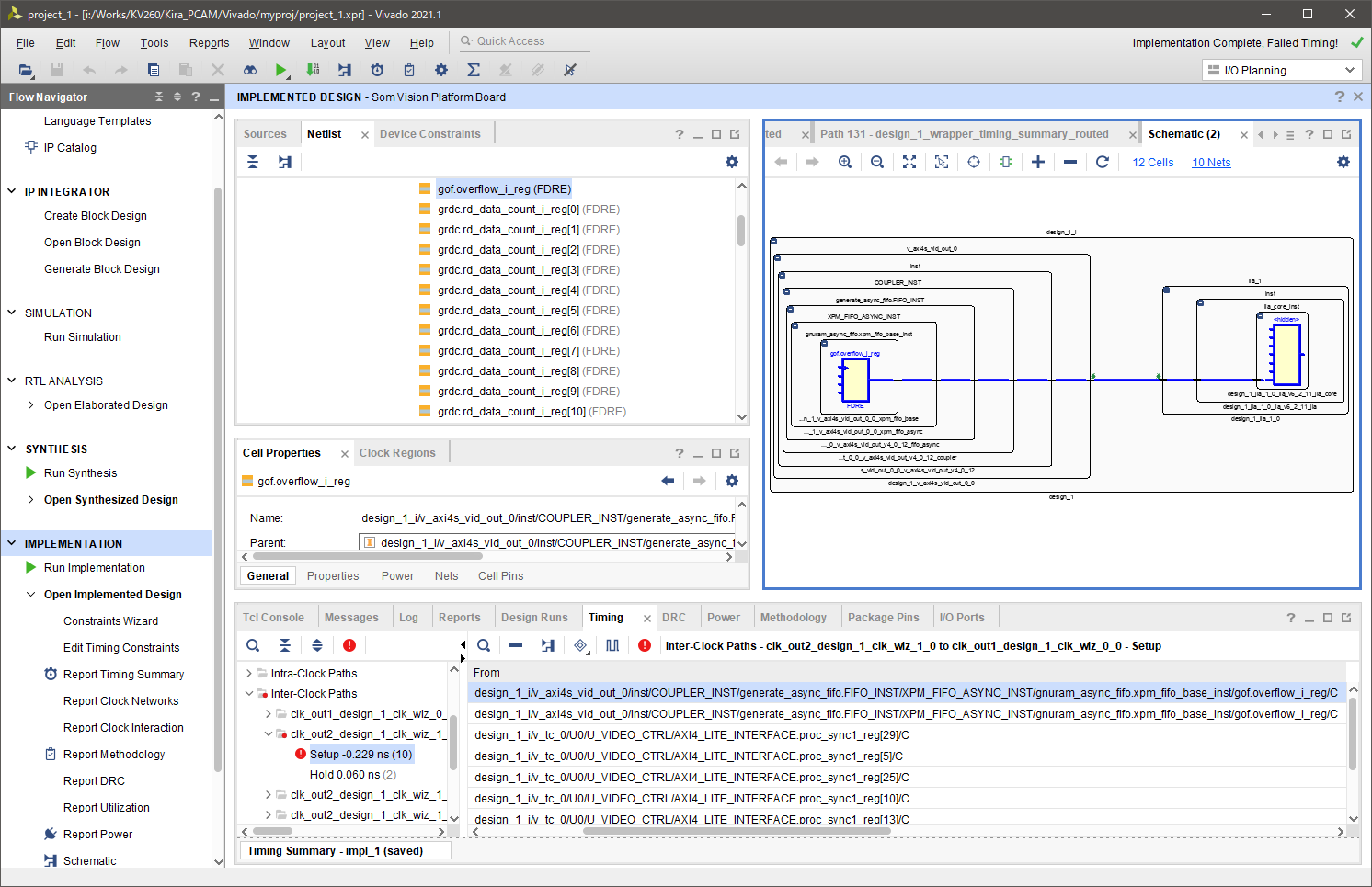

MicroZed Chronicles: Kria & Raspberry Pi Cameraをやってみる1はい、ここまでは FPGA の部屋の通りです。で、マイナスのスラックが出ます。

これも FPGA の部屋の通り、reset を追加します。で、ここ私は配線をちょっと変えました。reset の配線。

でインプリメンテーションまで実行するとこれも(:a :href "https://marsee101.blog.fc2.com/blog-entry-5379.html" ""MicroZed Chronicles: Kria & Raspberry Pi Camera”をやってみる2")の通りちょっとマイナスのスラックが出ます。(リセットを変えたので微妙に違う)

どの配線がまずいか?を追っていきたいのですが、hidden とか表示されていてどこだかわかりません。折角なので Vivado で回路を追っていきました。hidden 何かと思ったらila1 でした。

そこで、ila1 のクロックをいったん削除し、そうすると Vivado のお勧め配線が出るのでそれに従い配線をお願いします。

どうやら Zynq UltraSCALE+ が出力する dp_video_ref_clk に繋がなければいけなかったようです。

Linux で実行

実はここまで Windows でやっていました。その先の Vitis を Windows でやろうとしたら出来ませんでした。仕方がないので Linux で実行。

うまくいきました。