U50 用の Ether まわりの活用方法を模索していたら、たまたま、知り合いから Xilinx の github にある情報を教えてもらったのでそれをコンパイルした。

github から clone

xup_vitis_network_exampleからまずはサンプルを clone する。次に 100G-fpga-network-stack-coreも該当するディレクトリに移動して clone。

私の環境が Vitis 2021.1 なので 100G-fpga-network-stack-core だけbranch の vnx-vitis-hls を checkout。

ライセンスを取得

100G の Ether の IP は Xilinx の無償ライセンスが必要なので予め取得して置き $HOME/.Xilinx へコピーしておく。

コンパイル

100G-fpga-network-stack-core が xcu280 専用になっているのでトップの Makefile を書き換える。

これであとは xup_vitis_network_example のトップで make すればできあがる。DESIGN は benchmark を選んだ。basic というのもあるらしい。INTERFACE はU50 の場合1つしか口がないので 0 を指定する。

エラー

ライセンスがないとエラーになる。

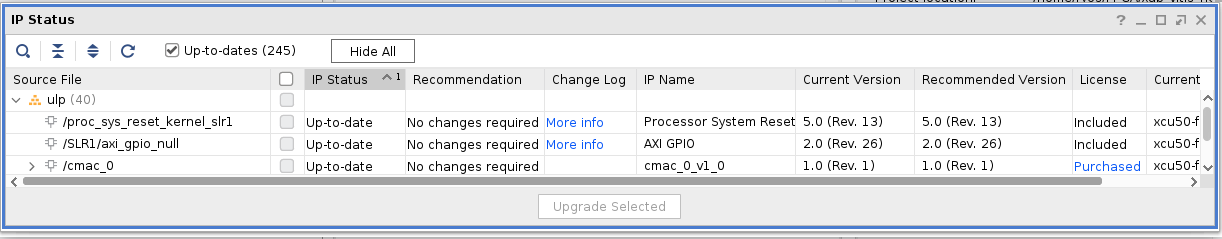

ライセンスが通っているかどうかは benchmark.intf0.xilinx_u50_gen3x16_xdma_201920_3/link/vivado/vpl/prj/prj.xprの GUI を立ち上げて IP Report を見ればわかる。Purchased なら OK。

関連する Xilinx の情報:[AR58758](https://support.xilinx.com/s/article/58758?language=ja)

テスト!!

さぁテストだ。とおもったら QSFP28 のケーブルを含む 100G の環境がない。この環境を構築しようと思ったらうん十万円の出費になりそう。

とりあえず fs.com で次の二つを購入

- QSFP28 100G 用 loopback コネクタ

- QSFP28 を SFP+ へ変換するコネクタ

テストはそれが来てから

おまけ

コンパイルしてできる xo は次の通り

これを実行する host プログラムは、、、どうやら python のみたい。Notebooksの下に ipynb などがある。

このプログラムどうやって QSFP28 の口を見つけているかというと、、、v++ にはその機能がない!ので tcl で書いている(らしい。要確認)

post_sys_link.tclこれを理解すると LED とか簡単に使えるようになる、、、かもね。書く xo の(CU の) connectivity は config_files の下にある。これでどう接続されているかがわかる。やっぱり AXIS しかないのね。あと SLR のどっちに配置するかもここに書かれている。

100G-fpga-network-stack-coreこれ面白そうね。TOE とか HLS で書いてある。かなり使えそう。