xilinx の RTL Kernel なるものをやってみることにした。Vitis で環境を作って、Vivado を立ち上げて、Vitis に戻って評価する。ターゲットは U50。

ここでやっていることは Using the RTL Kernel Wizard。謎の部分はいっぱいある。

注意点は KVAdd (A, B, Res) とかいいながら、A, B, Res に 1 たしているだけ。Res <= A + B をしているわけではない。

Vitis の起動

まずは Vitis の起動から入る。Vitis から RTL Kernel Wizard が呼べる。このウィザード。便利なのか、便利じゃないのか、、、複雑なプログラムを複雑に作ってくれるので、後から Verilog のソースをいじる気にならない。

とにかく、このページの通り作業を進めていくことにする。

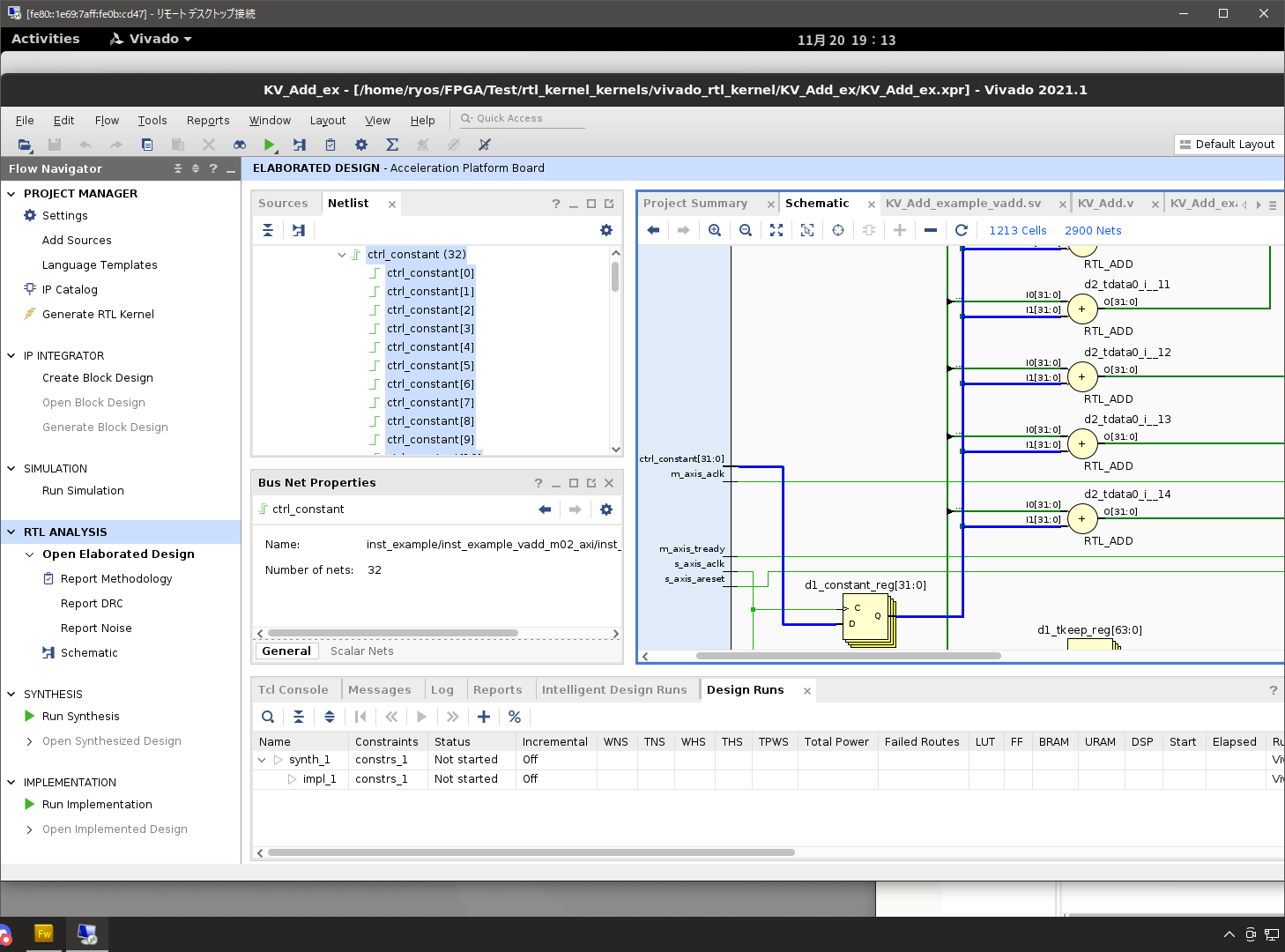

途中、Vivado が立ち上がって、Elaborate から回路図を見ろという風に書いてある。しかし、それ以上、の説明はない。

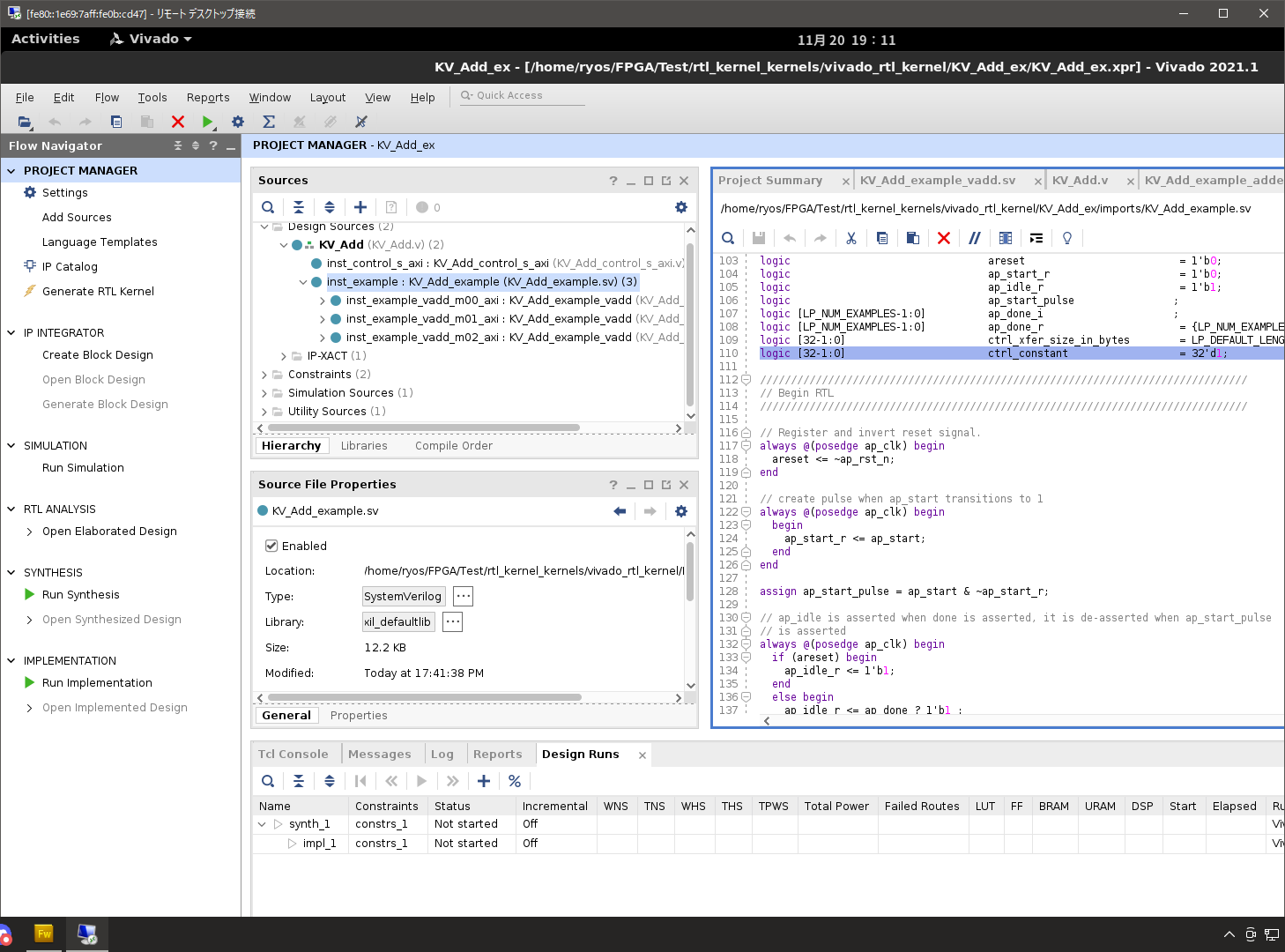

どうみても、ただ単に 1 足しているだけ。その後、Verilog のソースをみる。

どうみても、ただ単に 1 足しているだけ。ここでは掲載しないが、host のプログラムも各引数 A, B, Res に1 足されることを確認している。どうなってるんだ。scalar なるパラメタは設定されるが使われていない。

Vitis で確認

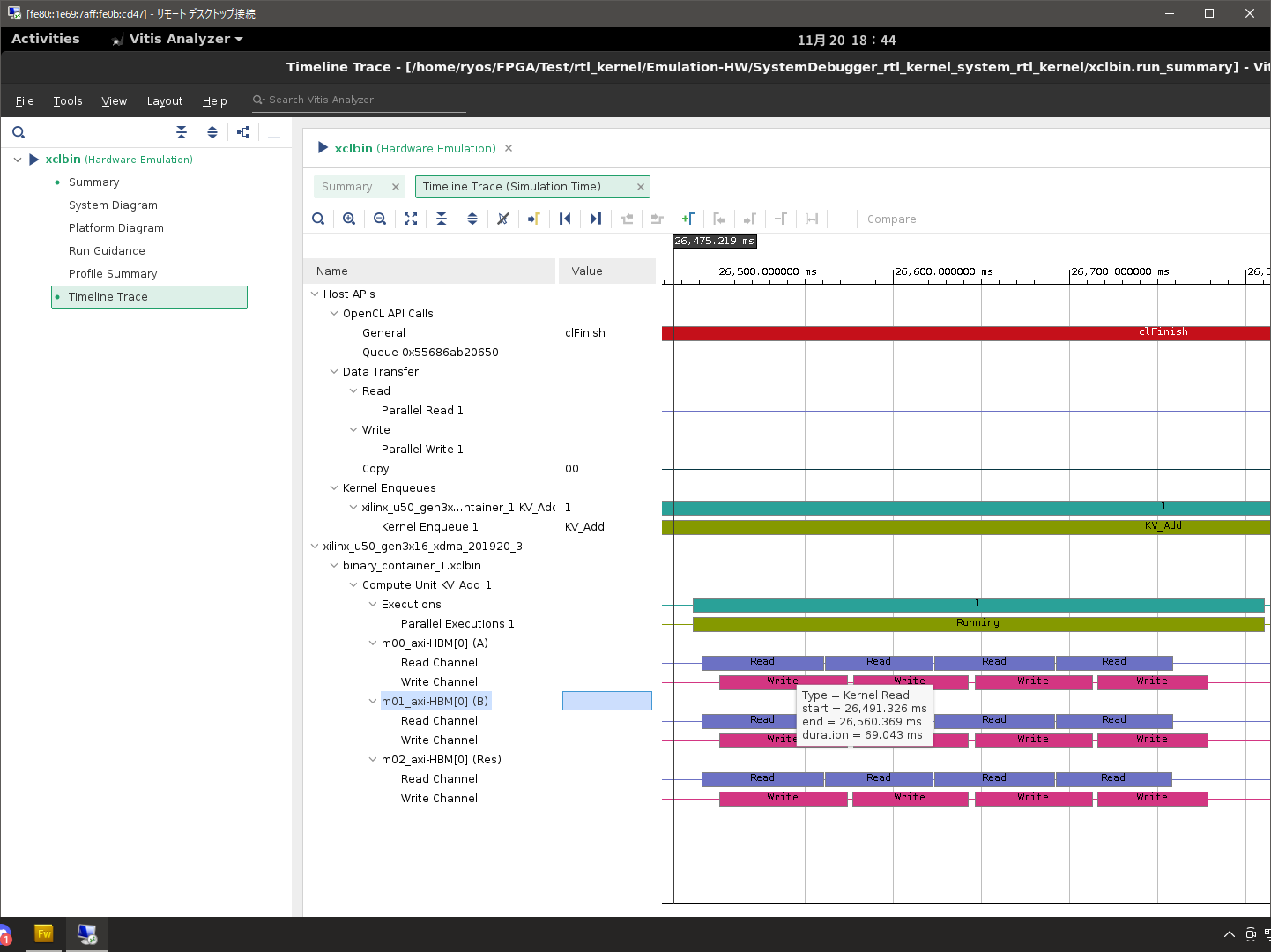

HW エミューレーションまで進むと、実際に HW が無くてもxsim でシミュレーションしてくれる。ちょっと便利ポイのが Timeline Trace。

AWS で実行した訳ではないのでちょっと結果が違っている。U50 は HBM2 だからかな?

XPM_FIFO_AXIS

自動生成してくれるソースの中で AXIS I/F の FIFO を使っている。これこれ。これがないと、真ん中の RTL が生きてこない。ug974 をみると "ファミリ: 7 シリーズ、UltraScale、UltraScale+"と書いてあるので、まぁ最近のチップは全部使えるみたい。

今後これを使うといいよね。

RTL Kernel って、今までの自分の資産をここに持ってこようと思っているのだから、Wizard で中途半端にソースを自動生成してもらっても、役に立たないよ!!