お絵描きだけしていると本質を理解しないのでCMOS とかレイアウトのの原理を理解していこう。

まずは用語

さらに現在参加している OpenRule1um で使われているローカル用語。KLayout をなんの設定もせずに立ち上げると、レイヤー情報もないようなのでそういう意味では POL とか DIFF なんてのもローカルな用語とも言える。

nsubcont は N-Well につながるダミーセル。そういう意味では nwellcont という名称のほうがより正確かもしれない。ダミーセルのダミーの意味は、あとでこれらの情報から本当の設計プロセスに関連する情報に書き直すためと思われる。こうすることで、通常の設計プロセスにまつわる NDA 問題を回避している。

DIFF は拡散層の意味だが、N あるいは P になる。どうやら、その指定のためにNarea, Parea があるようだ。さらに dcont というダミーセルを使って、その N-Diff あるいは P-Diff の領域を決めているのだろう。DIFF だけだとつながっているように見えるからね。

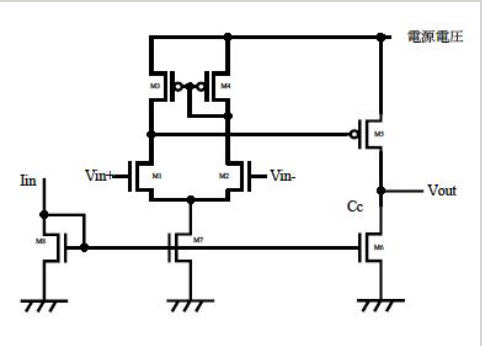

コンパレータ

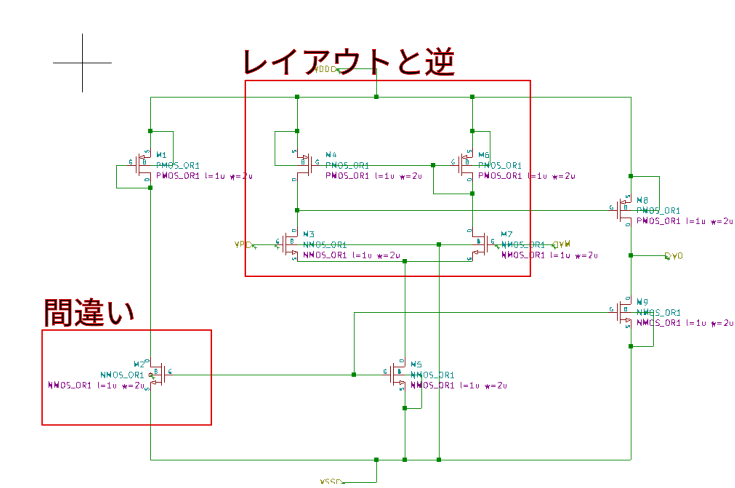

KiCad の回路図はすぐにできた。すぐにできたと思ったら、回路図間違ってた。

もとにした回路図はもはやどれかわからないが、基本的には非常にベーシックなものなので、教科書通りだと思う。

参照したのはこの回路Iin がよくわからんが、I だけに電流なんでしょう。

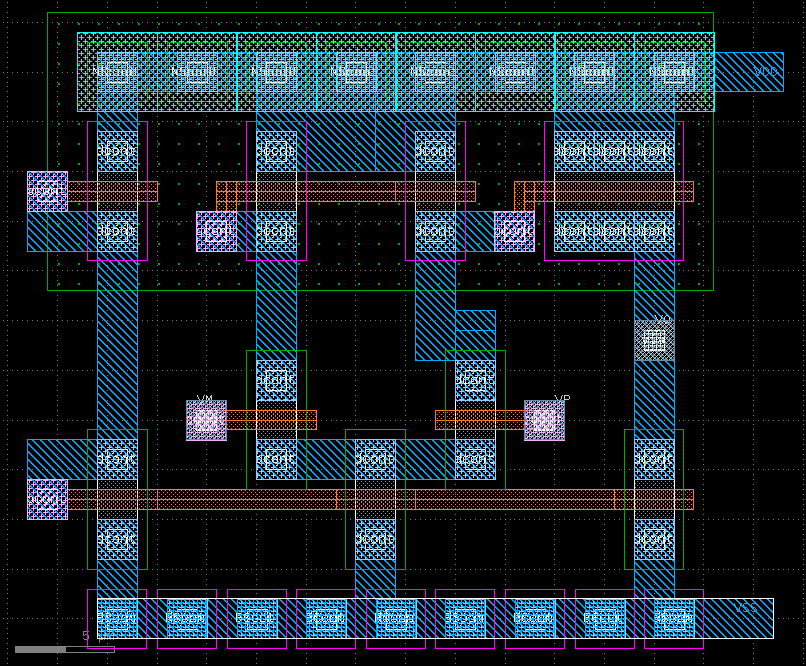

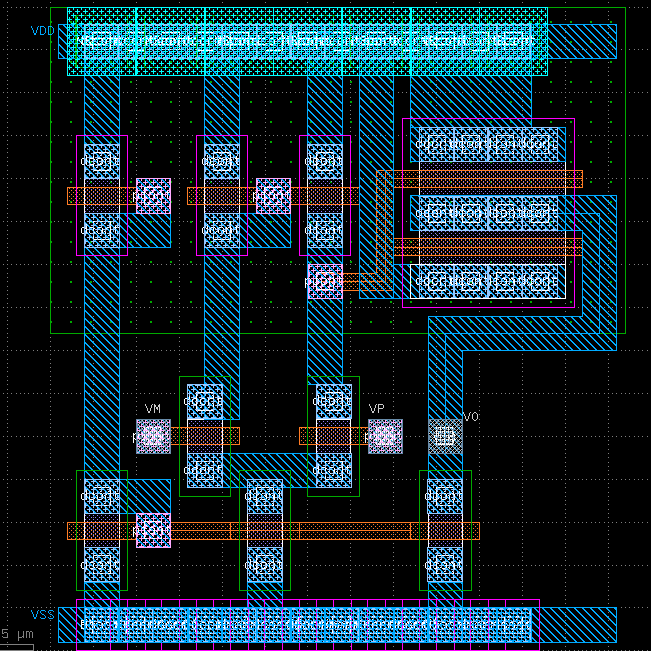

回路レイアウトは作業が細かくものすごく疲れる。KLayout で数時間かかる。

レイアウトの最後にはテキストを追加する。VDD と VSS のテキストは ML1 に VM と VP のテキストは ML2 に配置する。これも OpenRule1um のローカルルールのようだ。おそらく LVS を通すときに使われるのでしょう。

このルールから推察するに、Via を通すと ML2 に貫通して信号線を外に出せるのかな?

とりあえずできたと思いねぇ。DRC 通してみよう。げ!いっぱいエラーが。でも、エラーをクリックすると該当箇所の GUI に飛ぶので修正しやすいかも。

DRC, LVS ではいろいろ引っかかる。

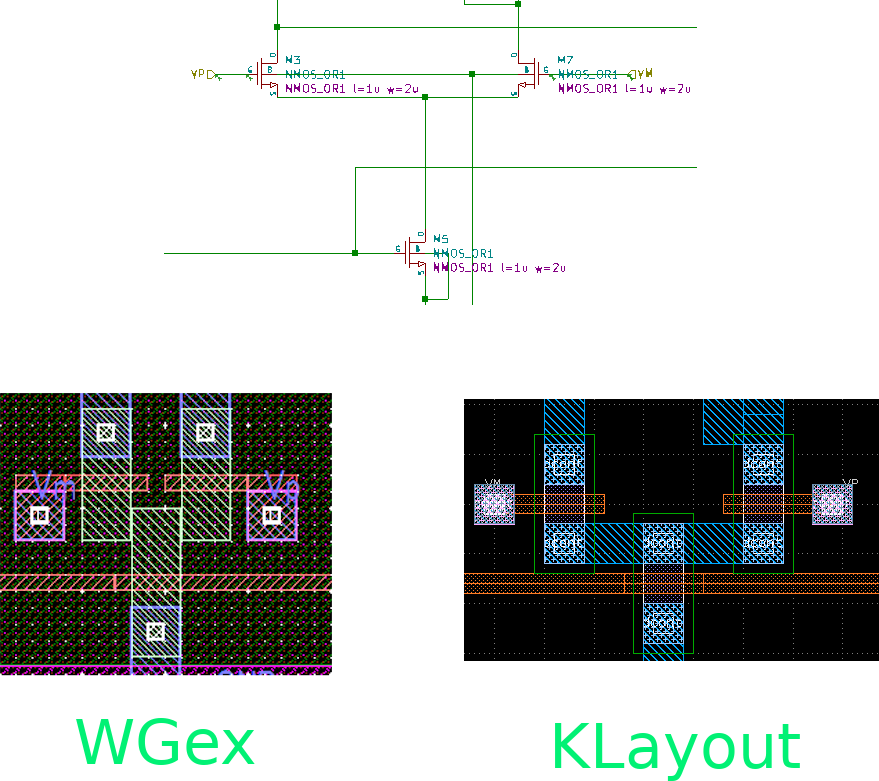

たとえば、WGex でコンパレータを作るを見ると、NMOS が横に連なっている回路のレイアウトは DIFF が重なっている。ところが KLayout の OpenRule1um の LVS ではこれがどうも NMOS と判定されないみたい(あるいは DRC で引っかかったか、、、うろおぼえ)。なので、離して配置することにした。

回路図を素直に書くとすべて w=2u になる。おそらく最終段だけ電流を多くしたいという意図から、レイアウト上は PMOS が去年は w=17u、今年はなぜか w=6u となった。6u で本当に動くかどうかはわからない。

参考までに書くと 17 は ((4 * 2) + 0.5) * 2 で 17。どういう計算? 0.5 はどこから出てきたのだろうか?二段になっているからかな?

その他、KLayout のバージョン違いや、KiCad が生成する OpenRule1um のライブラリを使った netlist の出力とKLayout の OpenRule1um の用意している LVS の不整合があり(なんでよ)、LVS 時に netlist から _OR1 の文字を削る必要があった。といった問題等に遭遇するも、なんとか解決し、回路レイアウトを完成させる。