MakeLSI 2021振り返り

2022-8-16 16:59 JST

MakeLSI 2021 年を振り返る。よくわからないなりに成功した(ということにしておく)。

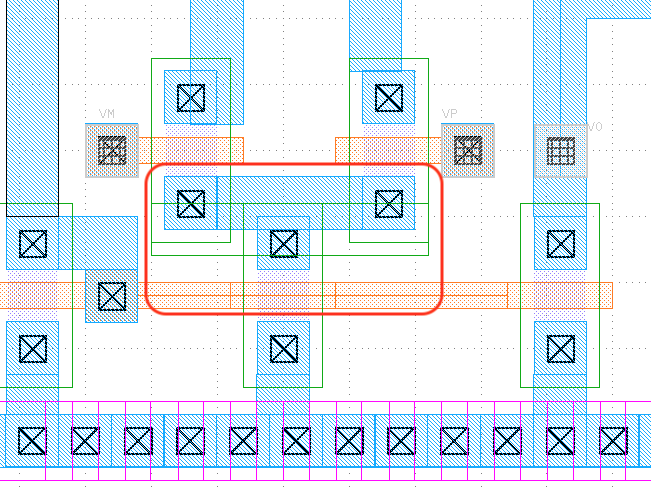

NMOS x 3

秋田先生の指摘で NMOS を配置したときに Narea の間が 0.5um だと、製造先のフェニテックのルールに反するらしい。DRC のチェックはそこまでしてなかったらしい。つなげてしまうと問題ないそうなので秋田先生が自ら直してくれました。ありがとうございます。

なお、2022 に似たように Comparator を作ると、見事 DRC のチェックが効いて(素晴らしい!!)、1.5um あけないとエラーになりました。

自分の Cell

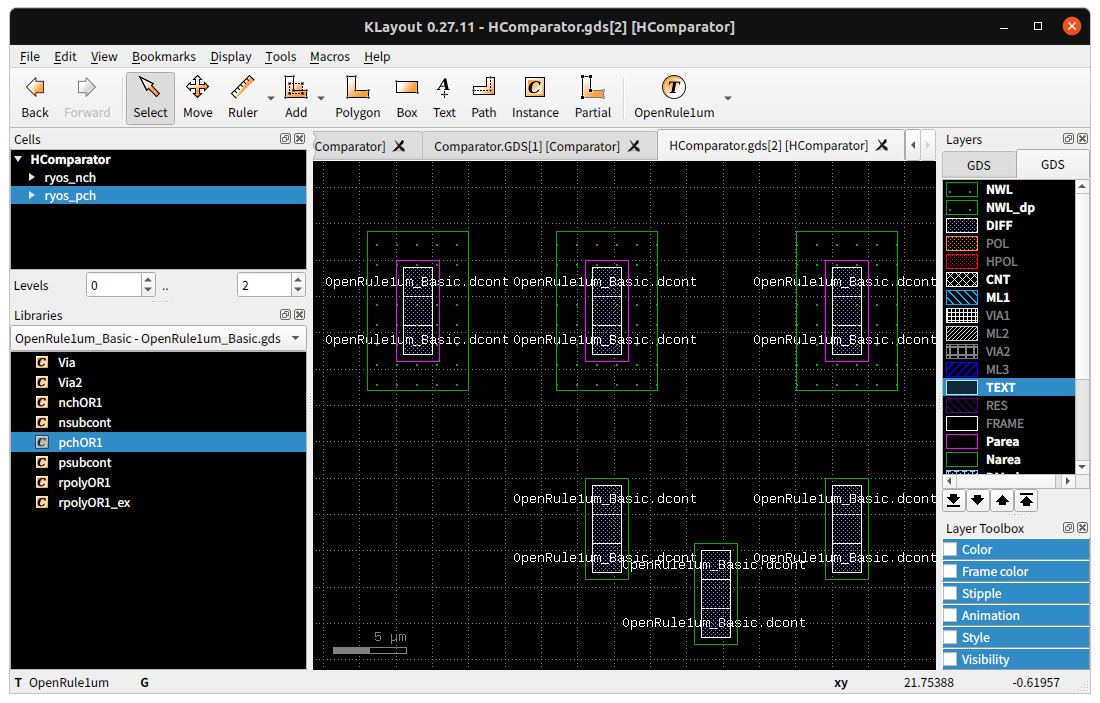

KLayout で自分の Cell を作ることができる。どうも、Cell を用意していない理由は階層になってしまうからみたいだ。最後に自動で製造先のルールに変えるので階層化されているといろんなことを考慮しなければならず、ミスの原因になるからであろう。

自分で Cell をつくる際の注意は pch で NWL も書かないといけないこと。同じ Cell 内に NWL がないとうまく自動変換できないみたい。つまりOpenRule1um のローカルルール。