VCO の回路図をうまく構築できたので、その備忘録。

VCO 回路図

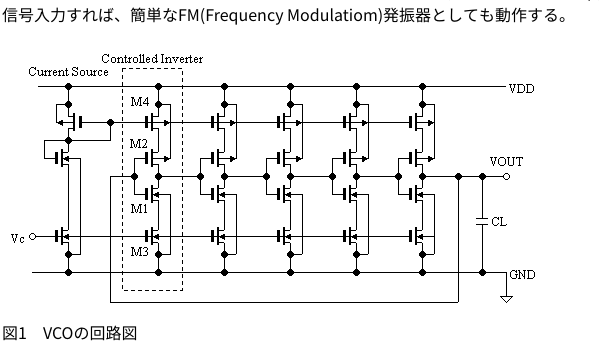

図1は金沢大学のウェブサイトから拝借してきた VCO の回路図である。これを KiCad に入力したのだけど、さっぱり動作しなかった。

よくみると、、、

なんかこれ、Base の接続とゲートの接続がごちゃっとしている。こういう書き方するの?おかしくない?

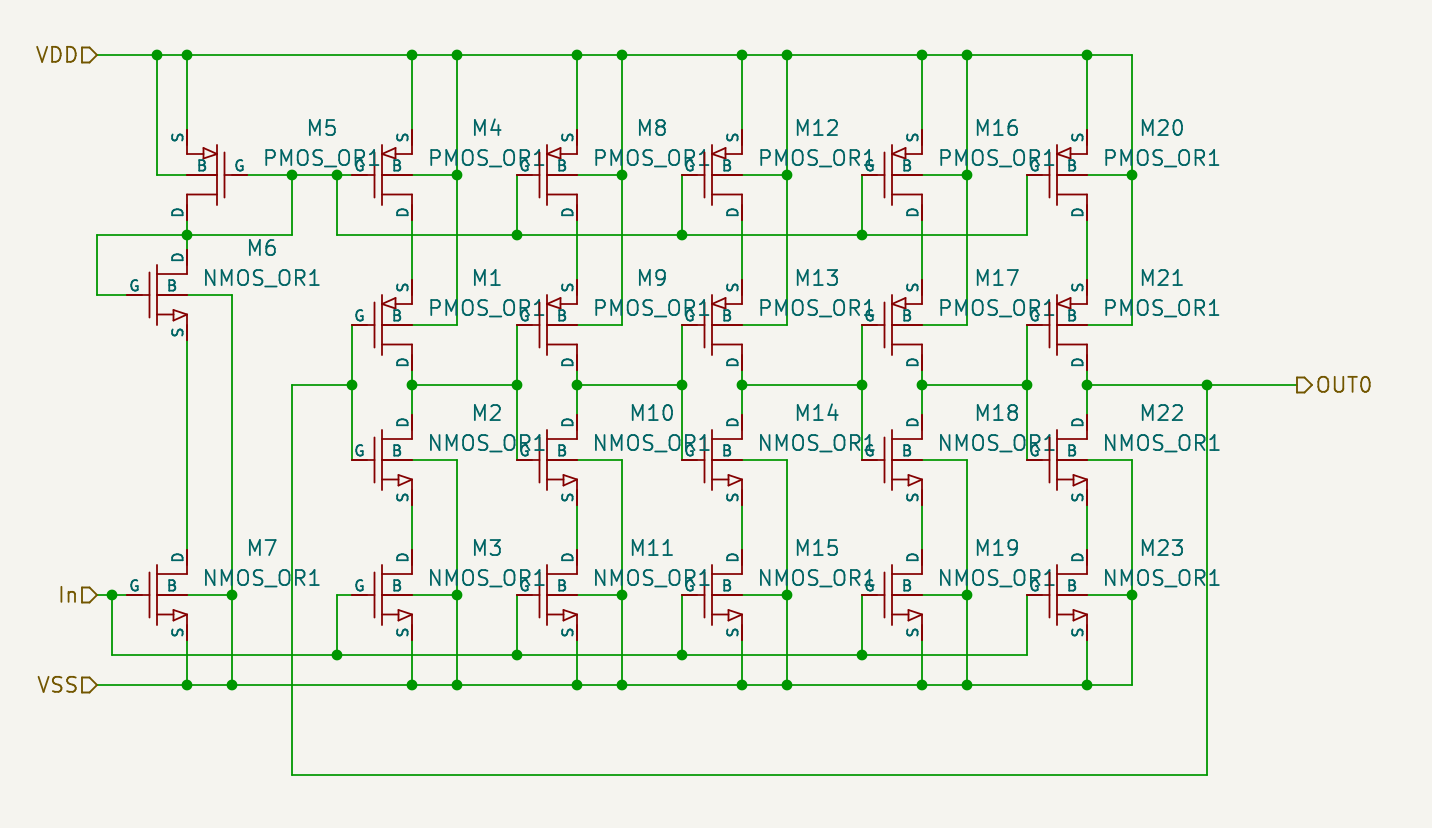

あ〜これなんとなくわかった。B がない CMOS のシンボルと B のある CMOS のシンボルが混ざっちゃっているんだ。

自分の理解で書き直してみる

Base の接続が変だし、Gate が突き抜けている、、、という謎の回路図になっていたので、PMOS の Base は VDD に、NMOS の Base は VSS にそして Gate をつなげてみることにした。

何だよ〜〜〜。うまくシミュレーションできるじゃないか。

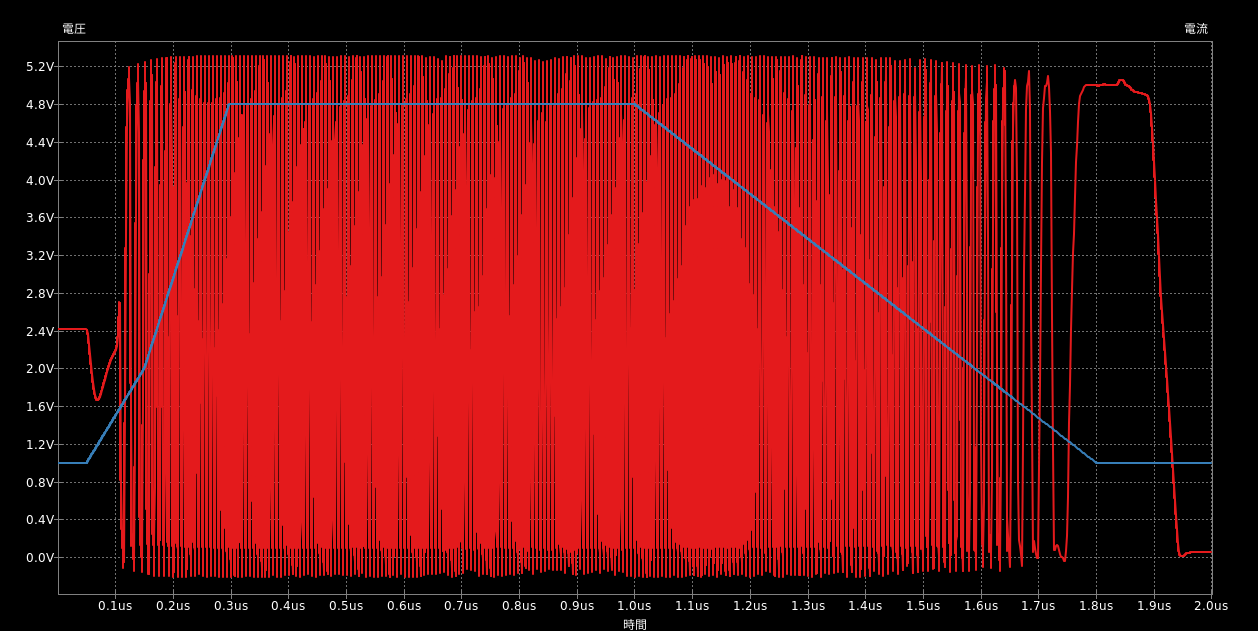

Inverter の遅延

結局、Inverter の遅延量を調整するのが VCO みたいだ。みるとわかるが与える電圧が高いほうが周波数が高くなる。与える電圧は Inverter の NMOS に影響する。例えば 1.2V 与えると 2.4V 下に引っ張られることになる。本当か?

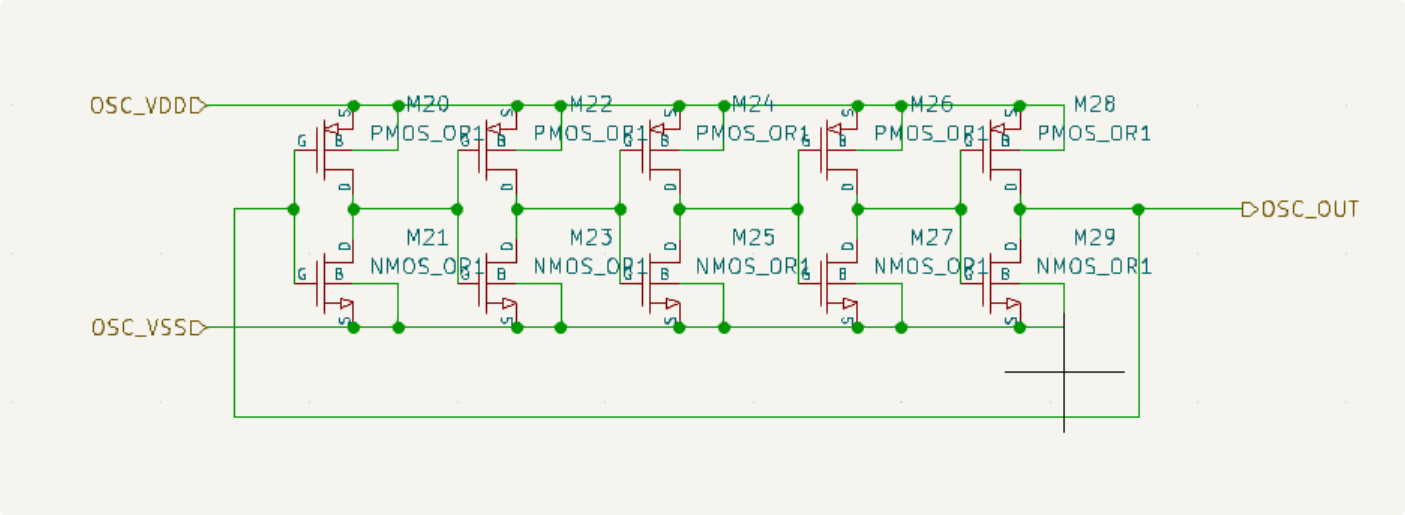

そこで、単純なリング・オシレータをつかってシミュレーションしてみることにした。

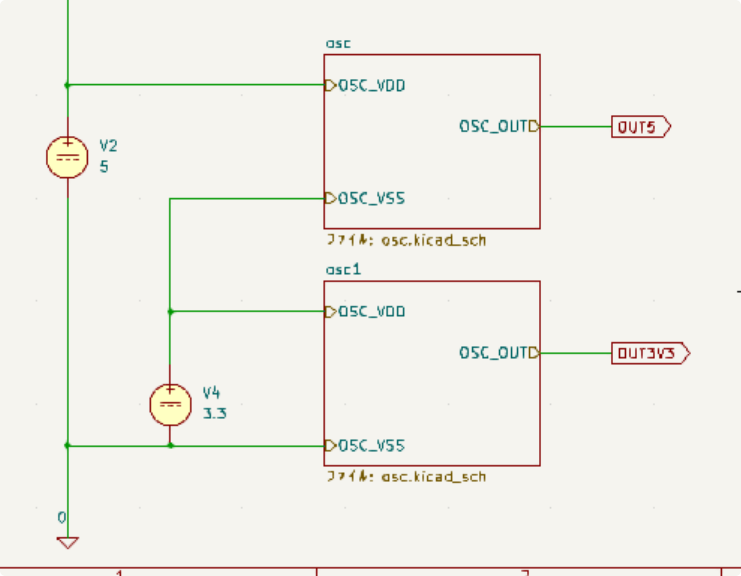

図のように作った簡単なリング・オシレータを階層シートにしてルートからコピー&ペーストで2つのシートを作った。そして、片方は 3.3V と 5V を与え、もう片方は 0V と 3.3V を与えた。

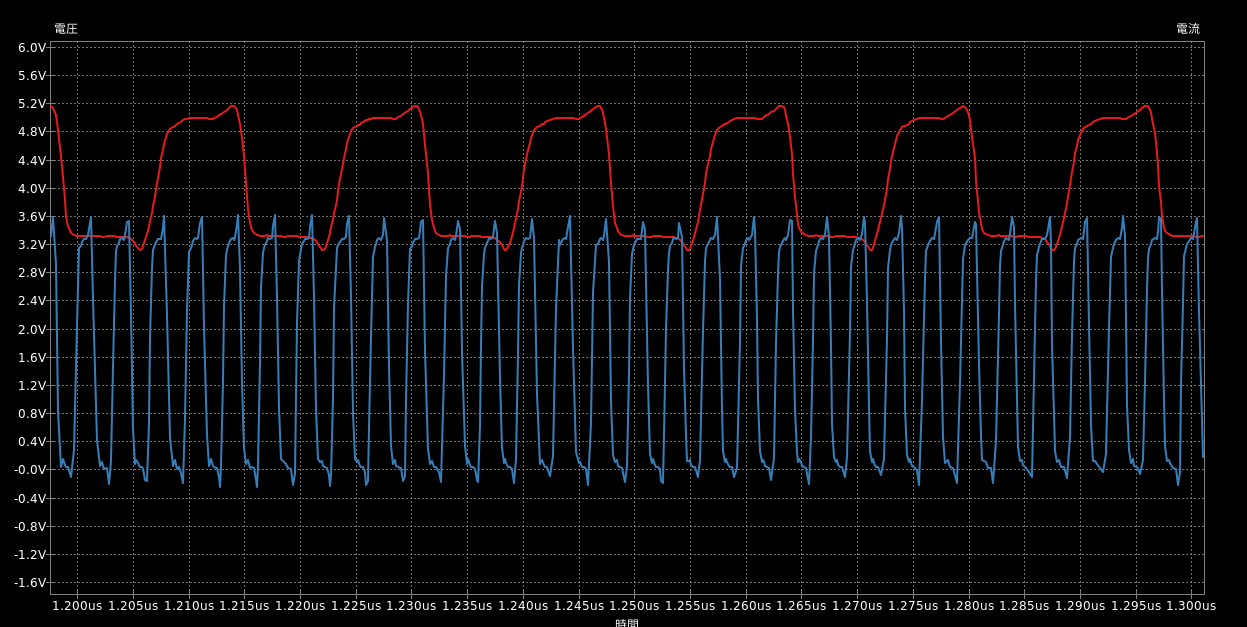

シミュレーションすると、電位差 1.7V (5V-3.3V) はゆっくりとした波形(赤)、電位差 3.3V は周波数が高い(青)という結果を得た。

電位差がある方が早くて、電位差がない方が遅い。一体なぜなのだ。

RC に還元される

「FPGA 時代に学ぶ集積回路の仕組み」という本の"CMOS 回路の遅延時間"という章に詳しく書いてあった。PMOS は無視して NMOS は抵抗、負荷にコンデンサがあるというモデルに置き換えることが出来るらしい。

あと立命館大学の資料がわかりやすかった。

それにしても KiCad がよく強制終了してしまうなぁ。