I2C と SCCB(Serial Camera Contorl Bus) の違いを検証してみました。

SCCB(Serial Camera Contorl Bus)

なぜここにあるのかは不明ですが、SCCB の仕様は 2.2 がいまのところ見つかっています。2.1 と 2.2 の違いは tCyc が min 10μs だったのがtypically 10μs に変わったこと。すごく遅いアクセスでも OK となったということだから、これでほぼほぼ I2C と同じになったのではないでしょうか?

オープンドレインではないということ

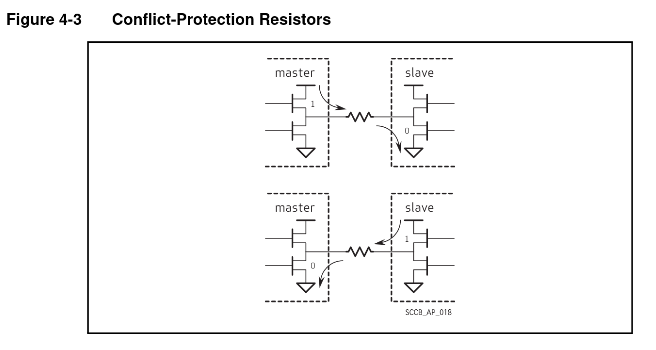

SCCB の仕様書から抜粋します。オープンドレインではないということはどういうことかというと、コンプリメタリ(相補)的な出力であるということです。相手が入力だけならいいのですが、SCCB のデータは inout です。そのため、運が悪いとホストの出力とデバイス側の出力がぶつかってしまいます。

何が起きるかというと、最悪のケースはショートしてしまうことでしょう。貫通電流というらしい。最悪のケースでは、一番脆弱な線が燃えてしまう恐れがあります。

ただ、FPGA の出力は電流の制限しているみたいで、ワイルドに LED 直結してもまぁ動くという例もありますから(推奨はされない)、なかなか燃えないようには出来ているみたいです。

I2C は ACK が必要

I2C はマスターがデータを送った直後にデバイスが即座に0をドライブすることで ACK を返したことになります。I2C はオープンドレインだからプルアップしているでしょう。つまりデバイス側がぼやぼやしていると1が返されてしまい、ACK を返したことになりません。その場合、ホスト側はエラーだと判断します。

SCCB は Don't-Care Bit

I2C のデータの変更はクロックが 0 の期間という規約があるため、デバイス側が ACK を出力するために入力から出力への切り替えるタイミングはシビアなケースがあるかもしれません。

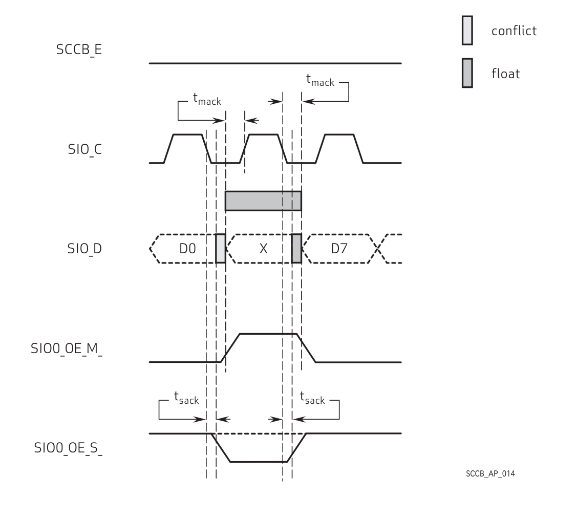

SCCB の規約では ACK に相当する期間は Don't-Care になっており、I2C に相当する ACK を返しても良いですし、ほっておいてもいい(float 状態にして良い)ことになっています。

SCCB の仕様書には コンフリクトしている(する可能性のある?)期間というのが定められています。

SCCB はここを何故変えた?

SCCB がなぜここのところを I2C から変更したのかという経緯は不明です。恐らく、対象となるのがカメラ・デバイスなので、SYNC 期間中にパラメタを迅速に変えたいという要求があったのではないかと予想しています。

その代償としてオープンドレインを捨てコンプリメタリな出力を受けるように設計しました。すると、出力のコンフリクト問題が発生します。そこで、ACK をドンドケアーにしてコンフリクトが起きない仕様に落とし込んだと思われます。

実際の動きはどうよ?

そうすると、実際の動きはどうなるのか気になります。Tang Nano 4K で OV2640 を接続して実験してみました。

ちゃんとキャプチャした画像じゃなく分かりづらいですが、8bit を送った直後(クロックの立ち下がり)と同時に黄色のデータの電圧が少し下がっています。

電圧が下がっているのは FPGA の出力が 3.3V でプルアップが 2.5V だからです。

これはホスト側が入力になって、デバイスもドライブしていないため、プルアップ電圧が観測された為でしょう。その後、データは 0 にデアサートされ、クロックの立ち下がりのタイミングでまたプルアップ電圧(と思われる信号)が観測されています。

つまり Don't Care のタイミングで OV2640 はちゃんと 0V をドライブし、なるべくはやく入力に切り替えるという動作をするようです。もしかして、Don't Care をフロートにする機能があるかと公開されている、仕様書をチェックしましたが、それらしきレジスタ設定はありませんでした。

時間が前後しますが、6bit 目と 8bit 目は 1 を出力しており、その直前のクロックがデアサートされている丁度まんなかでデータを 0 から 1 へと変更しているのもわかります。

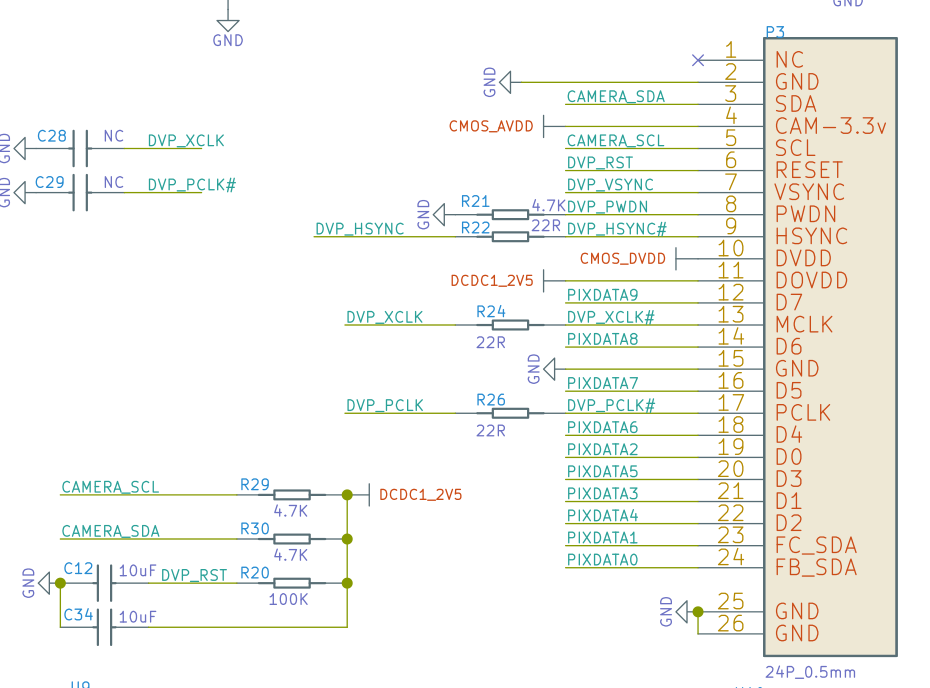

回路図を見る

今度は実際の回路図をみてみましょう。Tang Nano 4K の回路図を本家から抜粋します。

4.7K でプルアップしています。保護抵抗はつけてません。意外とそういうものなのかもしれません。

シミュレーションしてみる

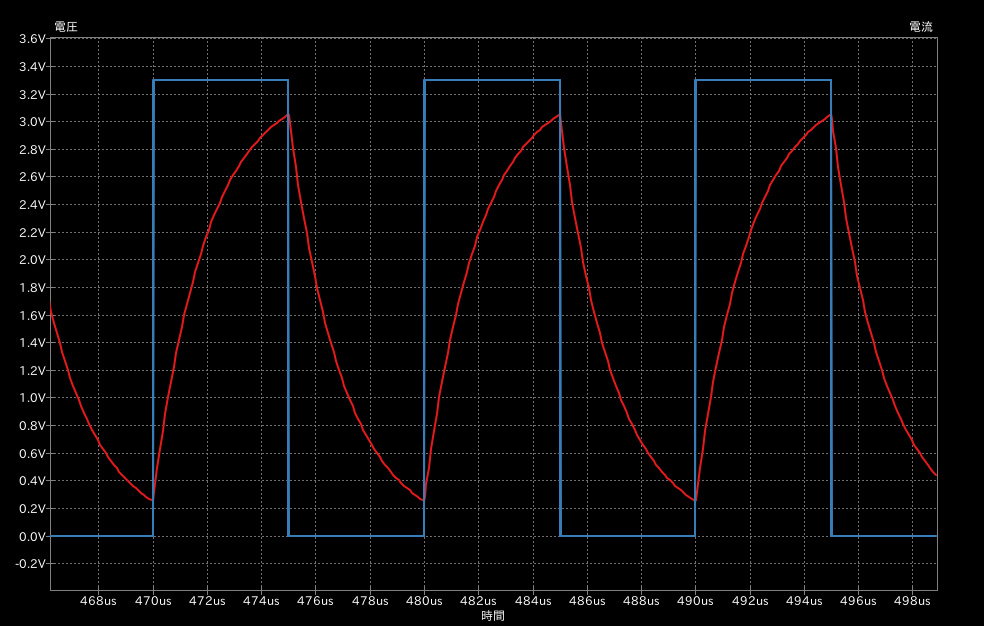

spice でシミュレーションしてみます。

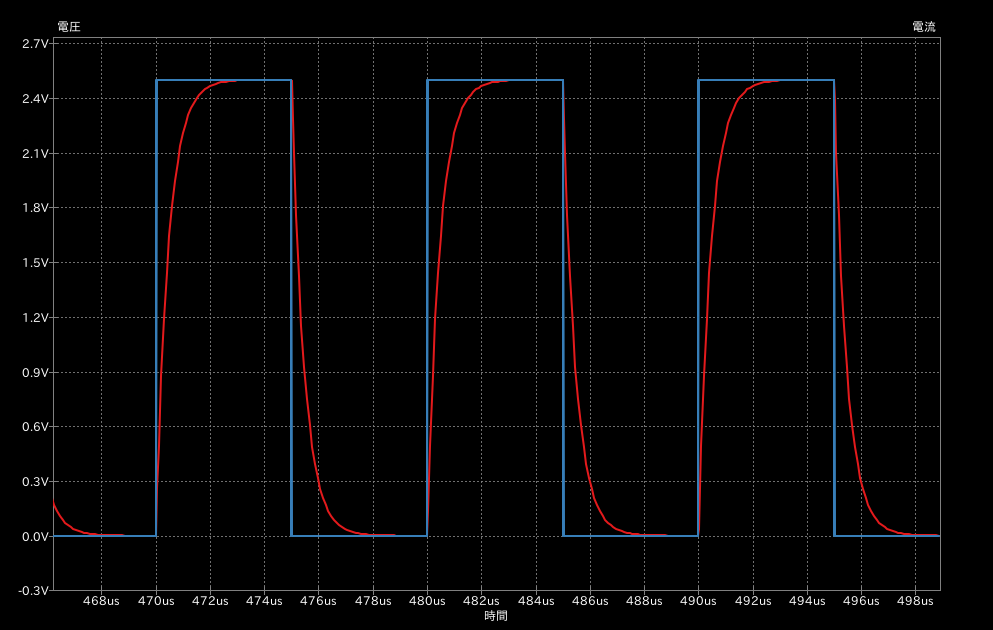

まずは 10k 200pF

10k 200pF でどれくらいのクロックに耐えうるか?を見てみます。

100kHz に間に合いませんね。ということなので、この手のクロックが関係する箇所はちゃんと寄生容量をみながら設計しないとちゃんとしたデータが取れません。ついでに 4.7k-100pf の例も。実際の波形と照らし合わせると、それほど寄生容量大きくないのかな。

貫通電流をシミュレーションしたかったのですが、うまくいきませんでした。後、レベルシフトもしたかったのですがうまくいかなかった。