JESD204C を使おうと思い PG242を読んでいる。

JESDC204C

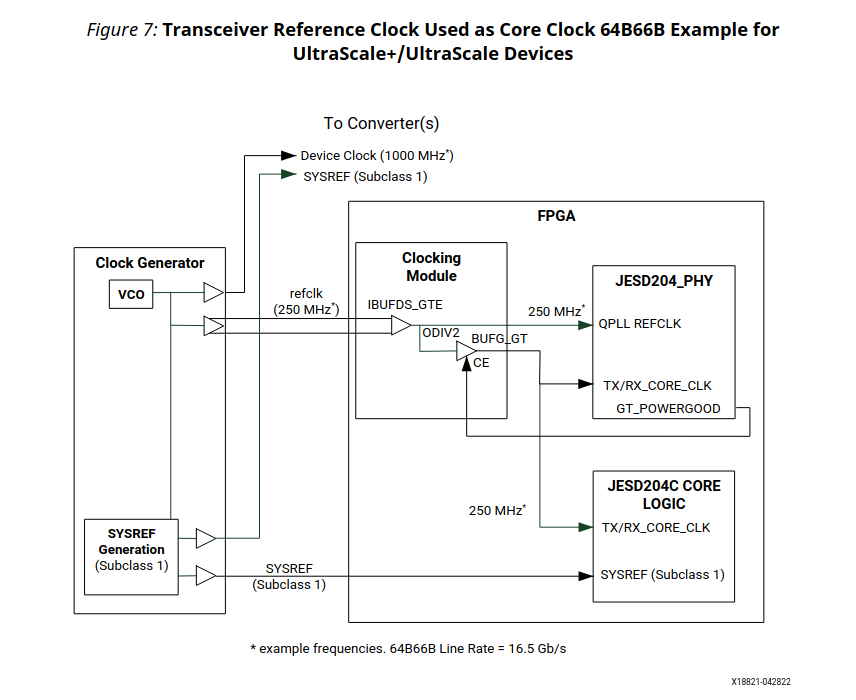

PG242 の figure をみると refclk を受けて、IBUFDS_GTEを使うようになっている。refclk は IBUFDS_GTE で分岐されて、core clock としても使われる。

ここまでは普通の GTE の使い方のような気がするが(昔 SDI の実装を手掛けたときにトランシーバを使ったことがある)、なぜか、SYSREF というものがある。そしてカッコ付きで subclass1 とある。

ADC/DAC の特殊事情

高速の ADC/DAC を使おうとするとそもそも1つのシリアルじゃ間に合わない。たとえば、2.5GHz の 12bit の DAC 出力だと、情報としては 2.5G x 12の帯域が必要。1本のシリアルとしては 30GHz の超高速になってしまうので、複数のシリアルに分けて FPGA と DAC 間の通信をする。その規格が JESD204 というわけだ。

このとき、DAC/ADC の特殊事情として「パワーサイクル間の遅延のばらつきを抑え、DACやADCとの決定論的レイテンシを保証する」という要求があるらしい。パワーサイクルというのは電源のON/OFFなどを指すようで、そのような状況になったとしても波形の遅延のばらつきを抑えるようにするということらしい。

どういう状況でそれが要求されるのかもわからないが、たとえば、440Hz のサイン波があった時に、電源の OFF/ON 後もそのサイン波が続いていたかのように波形の波の起伏が変わらないような仕組みだと思う(たぶんね)。位相制御とかいうらしい。

でもよく考えると、それだと 440Hz が予めわかっていないといけなさそうだ。本来、アナログ信号にはフレームないからね。どうも、JESD204 には同期用のヘッダがあるみたいだ。

JESD の subclass

そこで JESD では subclass というものを導入して、その遅延なるものを抑える機構を規定している。subclass0 は遅延を考慮しない。subclass1 は SYSREF でその遅延を制御する。subclass2 は SYSREF を用いずに sync 信号で保証する。

直感的には sync 信号で保証しない限りうまくいきそうにないが、subclass1 では SYSREF でできると言っている。中身はよくわかってない。TI の資料を読むとわかりそうな気がする(読んでない)。

どうも、SYSREF は refclk と異なるケースがあるようで、別途外部のモジュール(DAC とか ADC 側)からもらう必要がある。

手元にに JESD204C のDAC とかがないから試しようがない。