Vitis_Accel_Examples のサンプル実行と make 時に引き渡される引数の意味について解説します。

3部作になっています。

Vitis_Accel_Examplesの本家はこちら環境設定

XRT と Vitis の環境設定が必要です。csh では次のような感じ。bash だと source が.(ドット)になって .csh が .sh になる(でいいかな?)。

U50 で実行するには XRT がインストールされている必要があります。U50 の初期設定はこちら

まずはお試し

簡単そうな cpp_kernels の burst_rw を試しにやってみましょう。make コマンドを引数無しでたたくと使い方が出てきます。それを読むと all と run で使えることがわかります。次のように実行するとボードが無くても Xilinx の xsim というシミュレータ用のコードが出来て実行可能です。

make の時に重要なキーワードに TARGET と DEVICE があります。簡単に説明していきましょう。

TARGET

sw_emu, hw_emu, hw が選択可能。

sw_emu:ソフトウェアのシミュレーション。C++ レベルなのでコンパイルも実行も早い。 hw_emu:ハードウェアのシミュレーション。xsim が呼ばれる。 hw :実際のハードウェア。合成するのでバイナリを作るのがやたらと遅い。

DEVICE

DEVICE は正確には U50 を指します。最近の Xilinx の Makefile では PLATFORMに改められています。歴史的経緯でこの Examples では DEVICE になっているようです(どうやら最新のソースでは正確に PLATFORM という名称になったようだ)。SDAccel の延長の Vitis では PLATFORM を2種類定義していて(詳細はこの辺)「Vitis は、データセンターまたはエンベデッド プラットフォームのいずれかをターゲットとした FPGA アクセラレーション アプリケーションを開発するための統合フローを提供します」(Vitis フロー 101 チュートリアルより)だそうです。

データセンター

簡単に書くと Alveo とかはデータセンター(既存の SDAccel の延長)、それ以外の今までのボードはエンベデッド。データセンター用の PLATFORM は基本的にはベンダーからしか提供されない(詳細はブラックボックス)ようです。なので U50 で qdma が使いたくても(例えば Docker から仮想的にポートを見せたい!!なんて時はきっと qdma をつかう。つかったことないけど)、Xilinx が出してくれないと使えません。nodma なんてのも Makefile にキーワードがあるけど、実際の PLATFORM としては提供されていません。

データセンタ-は PCIe を含むブラックボックスの部分とユーザが作る部分に別れていてどうやら DFX(Dynamic Function eXchange) という技術、昔はパーシャルと呼ばれていた技術を使っているようです。

FPGA の部屋で DFX が紹介されているので([こちら](https://marsee101.blog.fc2.com/blog-entry-5296.html))、興味のある人は見てみるといいでしょう。

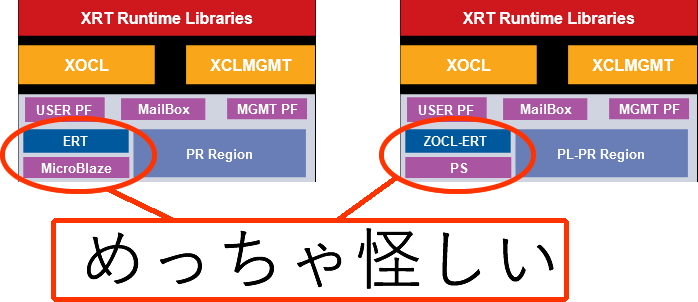

蛇足ながら XRT の [XRT and Vitis Platform Overview](https://xilinx.github.io/XRT/master/html/platforms.html) という資料に怪しい感じで PCIe Based Platforms に ERT とか MicroBlaze とか書いてあります。さらに PCIe Based Hybrid Platforms には ZOCL-ERT とか PS とか言う記述があります。

ERT を動かすためにベアメタルの環境が用意されているみたいです。U30 や VCK5000 では MPSoC があるので ZOCL-ERT が使えるみたいですね。今後のデータセンタの主流にするのかな?

エンベデッド

エンベデッドの方は SDSoC が廃止され(とほほ)、SDAccel 方式の OpenCL に統一された PLATFORM になりました。DFX は使用されていないようようです。(お~っと、ikwzm さんの XRT 環境は DFX つかってるぞ (:a :href "https://qiita.com/ikwzm/items/765dc4046746d35ef45c" "Ultra96/Ultra96-V2 向け Debian GNU/Linux で XRT(Xilinx Runtime)を動かす(2.8ビルド編)"))なので、データセンターとは違い、自分で PLATFORM を作る事が出来ます。KV260 で実際にやってみて出来ることを確認しました(いずれ記事で書きます)。

OpenCL 方式なので SDSoC のように関数をアクセラレートするという感覚ではなくなりました。すべてカーネルをロードして実行するというプログラミング・モデルです。

おまけ

v++ と xo

v++ で途中生成される xo(Xilinx Object) これなんでしょう?はい。zip でした。しかも、中身は cpp。RTL の場合は Verilog だったりします。

Xilinx の資料の中でリンクだのなんだのという言葉出てきますが既存の概念に合わせてるだけでまぁ一種のギミックですね。よくできた考え方なので不自然ではありません。

xclbin

v++ で作られる xclbin は hw, hw_emu, sw_emu で3種類あります。ヘッダーの中にそれを切り分ける情報があるらしく、hw の場合は単純に FPGA の bit ファイルです。hw_emu の場合は xsim で実行するための情報で、HDL のソースを含みます。sw_emu の場合は

それを XRT 用のランタイムが切り分けて実行します。正確には環境変数 XCL_EMULATION_MODE に TARGET を設定します。何も設定しないと hw の設定です。XCL_EMULATION_MODE を間違えると実行できないので、自動的に付けてくれる make から run するようにしましょう。